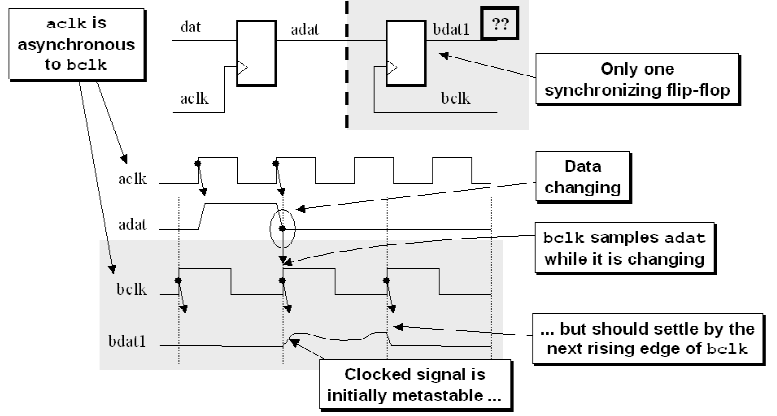

Metastability becomes a serious issue because a metastable output can propagate unstable or illegal signal values through the rest of the design.

🔁 Propagation of Errors

- A metastable output that passes through additional logic in the receiving clock domain can cause illegal signal values to spread.

- Since a Clock Domain Crossing (CDC) signal may fluctuate for a period of time,

- The input logic in the receiving domain might interpret the same signal as different values.

- This results in erroneous signals propagating throughout the system.

⏱️ Setup and Hold Times

Every flip-flop in a design has two critical timing parameters:

- Setup time: The minimum time before the clock edge when the data input must remain stable.

- Hold time: The minimum time after the clock edge when the data input must remain stable.

These timing constraints are defined to prevent data signals from changing too close to a clock edge, which could otherwise cause the flip-flop’s output to go metastable.